1. Tujuan [back]

1. Mengetahui berbagai teorema boolean.

2. Mengetahui bagaimana penggunaan berbagai teorema boolean.

2. Alat dan Bahan [back]

1. Gerbang OR

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

2. Gerbang AND

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali.

3. Gerbang NAND

menampilan nilai inverter dari input gerbang AND.jika output gerbang and berupa logika '1' maka pada gerbang nand outputnya akan menjadi logika '0'.

3.Dasar Teori [back]

Teorema Aljabar Boolean digunakan untuk menyederhanakan persoalan boolean dan juga untuk mengubah persamaan menjadi lebih berguna dan berarti dengan ekspresi yang sama. Teorema Aljabar Boolean dibagi menjadi 17, berikut pembahasannya:

1. Teorema 1 (operasi dengan '0' dan '1')

a. 0.X=0

b. 1+X=1

contoh:

0(A.B + B.C +C.D)=0 dan 1+(A.B + B.C +C.D)=1

a. 1.X=X

b. 0+X=X

dapat disimpulkan jika, 1.(ekspresi boolean) = ekspresi boolean, dan, 0 + (ekspresi boolean) = ekspresi boolean.

contoh:

1(A+B.C+C.D) = 0 + (A+B.C +C.D) = A+B.C +C.D)

3. Teorema 3 (Idempotent or Identity Laws)

a. X.X.X...X = X

b. X +X +X +•••+X = X

Teorema 3(a) memrepresentasikan AND gate.

Teorema 3(b) merepresentasikan OR gate.

4. Teorema 4 (Complementation Law)

contoh untuk teorema 4:

5. Teorema 5 (Commutative Laws)

a. X+Y=Y+X

b. X.Y=Y.X

6. Teorema 6 ( Assosiative Laws)

a. X+(Y+Z)=Y+(Z+X)=Z+(X+Y)

b. X.(Y.Z)=Y.(Z.X)=Z.(X.Y)

illustrasi teorema 6(a) dan 6(b):

7. Teorema 7 (Distributive Laws)

a. X.(Y+Z)=X.Y+X.Z

b. X+Y.Z=(X+Y).(X+Z)

Tabel pembuktian hukum distribusi:

Illustrasi hukum distribusi:

8. Teorema 8

9. Teorema 9

10. Teorema 10 (Absorption Law or Redundancy Law)

a. X+X.Y=X

b. X.(X+Y)=X

Pembuktian dari Absorption law adalah straightforward:

X +X.Y = X.(1+Y )= X.1 = X

11. Teorema 11

Tabel pembuktian teorema 11(a):

12. Teorema 12 (consensus Theorem)

Tabel pembuktian dari teorema 12(a):

13. Teorema 13 (DeMorgan's Theorem)

DeMorgan's Theorem dalam gerbang logika, logic High State:

14. Teorema 14 (Transposition Theorem)

Bukti dari Teorema 14 (a)

15. Teorema 15

16. Teorema 16

17. Teorema 17 (Involution Law)

a. Hukum Asosiatif

Saat gerbang OR pertama di beri logika '1' dan logika '0' maka 1+0 adalah 1 maka keluarannya adalah logika '1'. selanjutnya, saat keluaran dari gerbang OR pertama yang berlogika '1' masuk ke kaki gerbang OR2 dan kaki gerbang OR2 satunya diberi logika '0', maka 1+0 adalah '1', maka keluarannya berupa logika '1'

b. Hukum Distributif

Saat gerbang OR di beri logika '1' dan logika '1' maka '1'+'1' adalah '1' maka keluarannya adalah logika '1'. selanjutnya, saat keluaran dari gerbang OR pertama yang berlogika '1' masuk ke kaki gerbang AND dan kaki gerbang AND satunya diberi logika '0', maka '1'x'0' adalah '0', maka keluarannya berupa logika '0'

Saat gerbang AND1 diberi logika '1' dan '0', maka '1' x '0' adalah logika '0', maka keluarannya adalah logika '0'. dan gerbang AND2 diberi logika '1' dan '1' sehingga '1' x '1' maka keluarannya adalah logika '1'.

logika '0' dari keluaran gerbang AND1 masuk ke salah satu kaki gerbang OR, dan keluaran dari gerbang AND2 yang merupakan logika '1' juga masuk ke kaki gerbang OR. sehingga '1' + '0' akan menghasilkan keluaran berlogika '1

c. Hukum DeMorgan

saat gerbang NOR tiga fasa diberi logika '1' '1' '1' maka '1'+'1'+'1' adalah logika '1' tetapi karena gerbang nor memiliki komponen inverter sehingga logika '1' tadi di inverter hingga keluarannya menjadi berlogika '0'.

d. Teorema 17 contoh 1

Saat gerbang NAND1 diberi logika '1' maka keluarannya akan berupa logika '1'. saat gerbang NAND2 dibelo logika '1' maka akan diinverter hingga keluarannya berupa logika '0'. sehingga keluaran dari kedua gerbang NAND tersebut masuk ke gerbang NAND3 dengan logika di kaki gerbang NAND3 adalah '1' dan '0'. karena '1' x '0' adalah '0' dan diinverter sehingga keluarannya adalah logika '1'.

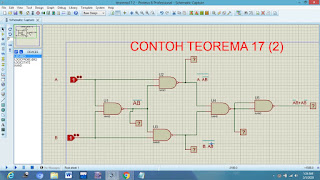

e. Teorema 17 contoh 2

Saat gerbang NAND1 diberi logika '1''1' maka keluarannya akan berupa logika '0'. saat gerbang NAND2 dibelo logika '1' '0' maka akan diinverter hingga keluarannya berupa logika '1'. dan saat gerbang NAND3 berlogika '0' dan '1' keluarannya akan berlogika '1'. logika yang masuk ke gerbang NAND4 adalah '1' '1' sehingga keluarannya adalah logika '0'. Logika '0' dari gerbang NAND4 masuk ke kedua kaki gerbang NAND5, sehingga logika masukan NAND5 adalah '0' '0', sehingga keluarannya adalah logika '1'.

5.Video [back]

6.Link Download [back]

Simulasi Proteus - download

Video Simulasi - download

download data sheet and disini

download data sheet nand disini

download data sheet or disini

Tidak ada komentar:

Posting Komentar